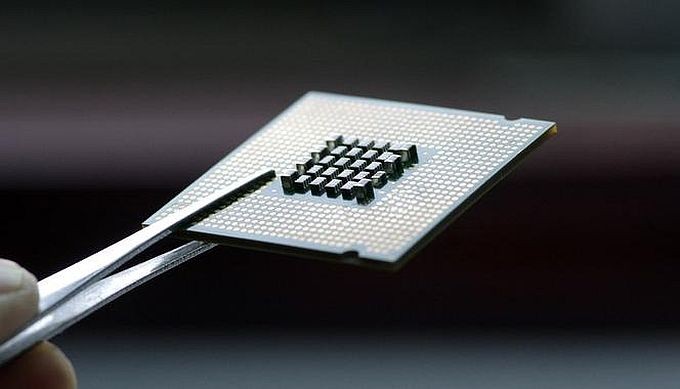

三星电子表示,目前正通过封装晶圆代工非记忆体半导体和高带宽记忆体的集成解决方案,研发高性能、低能耗的人工智能半导体产品,与现有工艺相比,从研发到生产的耗时可缩减约20%。具体技术路径为,三星电子将于2027年在2纳米工艺中采用背面供电网络技术(制程节点SF2Z)。该技术可将晶片的供电网络转移至晶圆背面,与信号电路分离,从而简化供电路径,降低供电电路对互联信号电路的干扰。若在2纳米工艺中采用该技术,不仅能提高功率、性能和面积等参数,还可以显着减少电压降,从而提升高性能计算设计性能。另外,三星电子还计划2027年把低能耗且具有高速数据处理性能的光学元件技术运用于人工智能解决方案。

三星电子认为,人工智能时代需要高性能且低能耗晶片。他们将通过和人工智能晶片适配度最高的环绕式栅极工艺、光学元件等技术适应这一需求。为此,三星电子将于2025年在4纳米工艺中采用“光学收缩”技术(制程节点SF4U)进行量产,可使晶片体积变得更小◆